Circuit design has been a game for big industry for far too long! Makerchip provides free and instant access to the latest tools directly from your browser and from your desktop. This includes open-source tools and proprietary ones. Turning the tables for the open-source community, Redwood EDA, LLC's commercial capabilities are often available for open-source development here first--before they are available commercially!

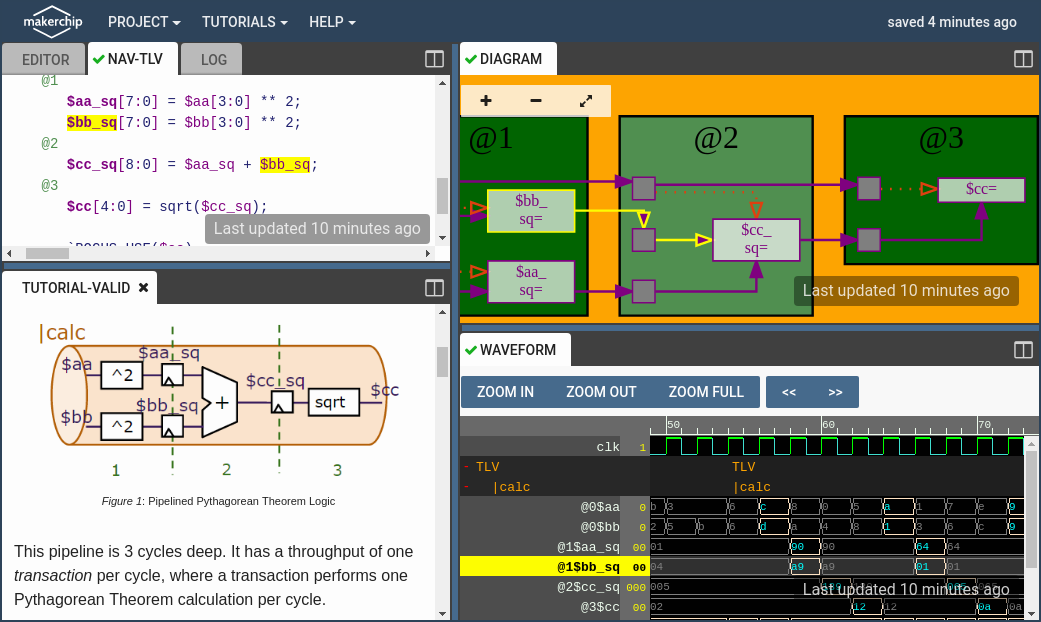

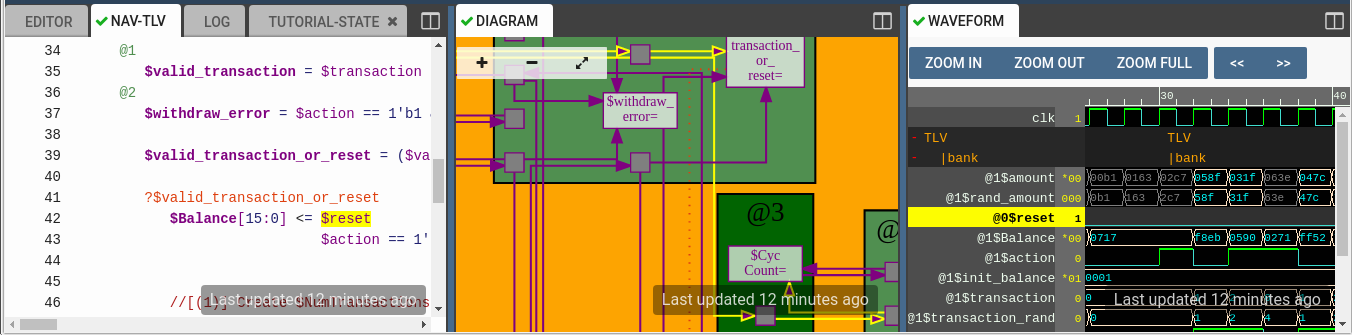

You can code, compile, simulate, and debug Verilog designs, all from your browser. Your code, block diagrams, waveforms, and novel visualization capabilities are tightly integrated for a seamless design experience.

While Makerchip introduces ground-breaking capabilities for advanced Verilog design, it also makes circuit design easy and fun! Tutorials will get you going.

Did we say "easy" and "Verilog" in the same breath? That's just contradictory! That's why it is so important that Makerchip supports the emerging Transaction-Level Verilog standard. Transaction-Level Verilog, or TL-Verilog, represents a huge step forward, by eliminating the need for the legacy language features of Verilog and by introducing simpler syntax. At the same time, TL-Verilog adds powerful constructs for pipelines and transactions. We'll help you learn it, and you'll never turn back! It's the easiest way to write and edit your Verilog with fewer bugs.

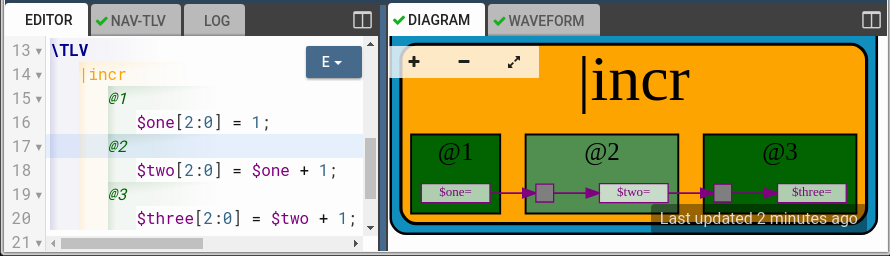

Here's a quick taste of TL-Verilog. (Not familiar with sequential logic? Try Wikipedia.)

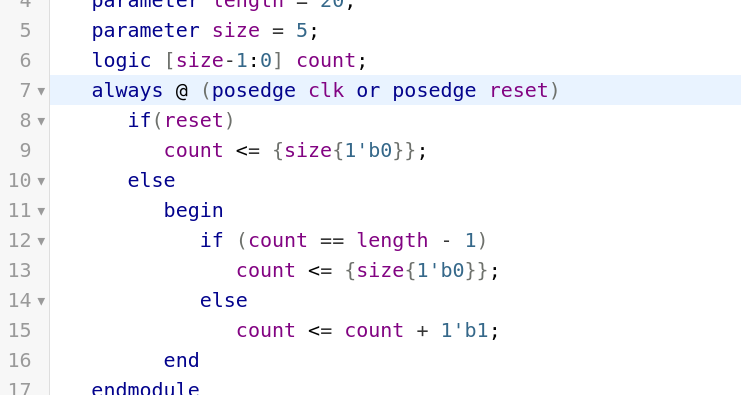

Instead of writing in Verilog always_ff @(posedge clk) begin ... to create flip-flops... don't write anything!

Organize your Verilog logic statements into pipelines, and let TL-Verilog

imply the necessary flip-flops.

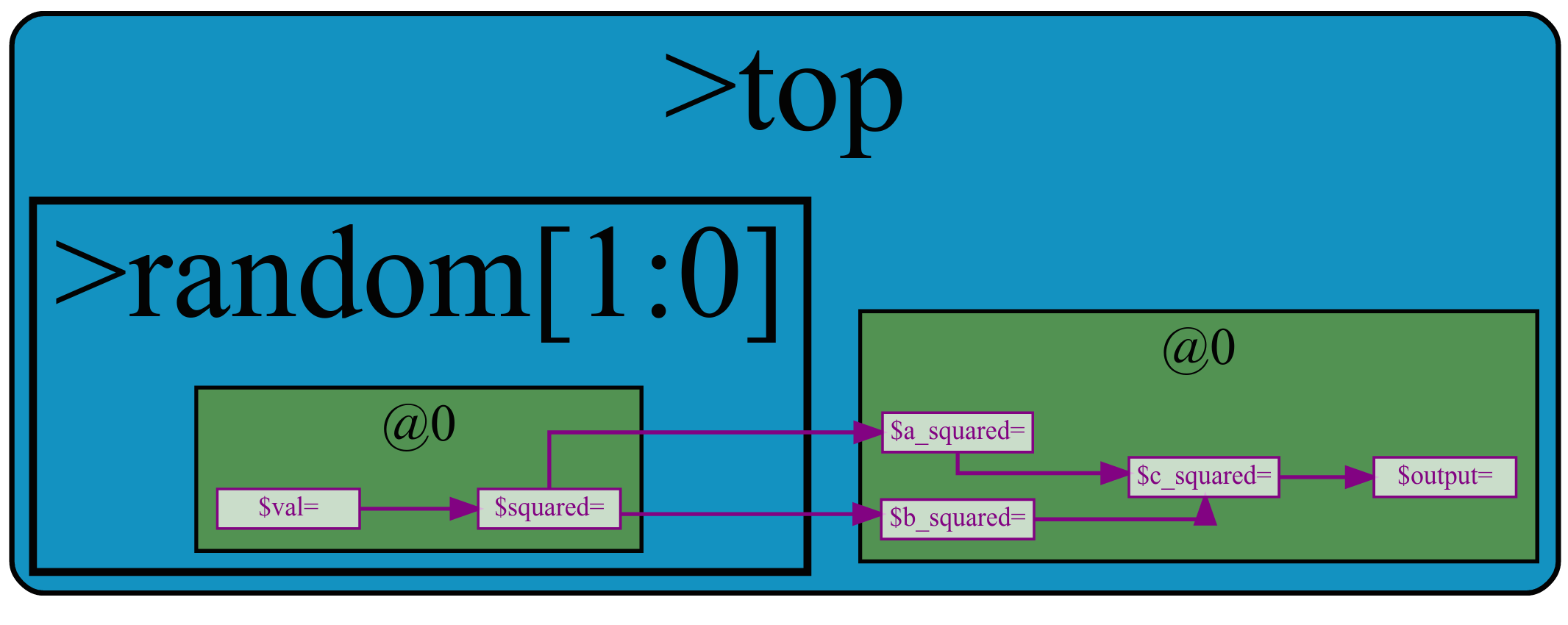

The code below provides a pipeline, called |incr containing

pipeline stages @1, @2 and @3. Each stage increments the value from

the previous stage by one in a subsequent clock cycle.

Flip-flops (represented as grey squares in the diagram)

carry values from one stage to the next.

In case you are curious, here's some corresponding Verilog code:

logic [2:0] INCR_one_a1, INCR_one_a2;

logic [2:0] INCR_two_a2, INCR_two_a3;

logic [2:0] INCR_three_a3;

assign INCR_one_a1[2:0] = 1;

always_ff @(posedge clk) INCR_one_a2 <= INCR_one_a1;

assign INCR_two_a2 = INCR_one_a2 + 1;

always_ff @(posedge clk) INCR_two_a3 <= INCR_two_a2;

assign INCR_three_a3 = INCR_two_a3 + 1;Pipeline context reduces bugs and makes your design easy to maintain in the face of timing changes.

Learn more about TL-Verilog pipelines as well as other powerful constructs, including hierarchy, state, validity, and transactions in the TL-Verilog tutorials inside the Makerchip IDE.

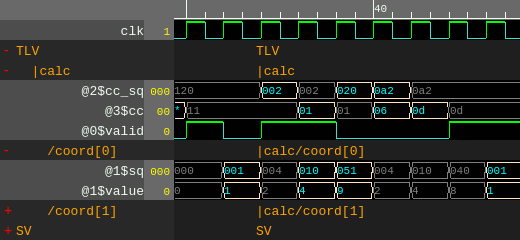

Waveforms are organized by TL-Verilog design hierarchy. Waveforms clearly show when signals are carrying meaningful data.

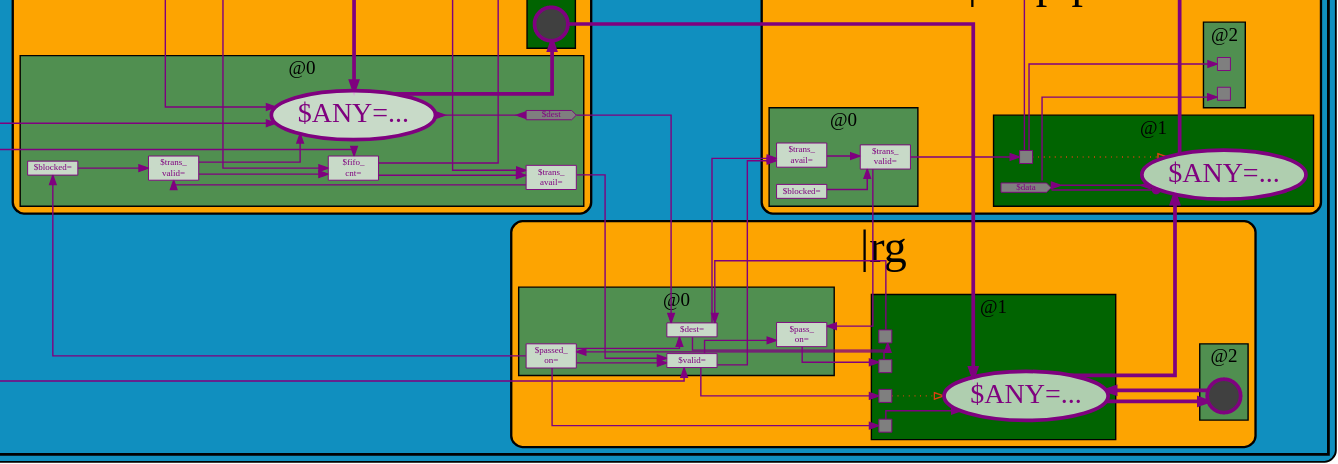

Your designs are represented in logic diagrams. TL-Verilog design hierarchy,

including pipelines and pipeline stages, provides organization to

your logic diagrams. Below, the path through $ANY ovals shows the

flow a transaction will follow through an example design.

TL-Verilog constructs in the code editor, diagram, and waveform viewer are all linked together. Clicking an element such as a signal in one view will highlight that element across all views.

Makerchip can easily be launched as a Verilog/TL-Verilog editor from other applications. For example, Makerchip provides the digital side of FOSSEE's mixed-signal eSim environment, and SandPiper-SaaS provides eSim's TL-Verilog compilation.